# Revision History 5GB & 10GB 3D pSLC eMMC v5.1 153ball FBGA PACKAGE

| Revision | Details                       | Date      |

|----------|-------------------------------|-----------|

| Rev 1.0  | Initial Release - Preliminary | May. 2024 |

Confidential -1 / 44- Rev.1.0 May 2024

# **Contents**

| 1. | PRODUCT SUMMARY                                                                                                                                                                                                                     | 3                          |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2. | PRODUCT FEATURES                                                                                                                                                                                                                    | 3                          |

| 3. | ORDERING INFORMATION                                                                                                                                                                                                                | 4                          |

| 4. | PRODUCT DESCRIPTION                                                                                                                                                                                                                 | 4                          |

|    | 4.1 PERFORMANCE SPECIFICATIONS 4.2 CURRENT CONSUMPTION 4.3 ENVIRONMENTAL SPECIFICATIONS 4.4 MECHANICAL SPECIFICATIONS 4.5 RELIABILITY AND ENDURANCE 4.6 DRIVE GEOMETRY SPECIFICATION                                                | 6<br>8<br>8                |

| 5. | PACKAGE MECHANICAL                                                                                                                                                                                                                  |                            |

|    | 5.1 Physical description                                                                                                                                                                                                            | 10                         |

| 6. | E-MMC DEVICE AND SYSTEM                                                                                                                                                                                                             | 12                         |

|    | 6.1 e·MMC system overview. 6.2 Pinout. 6.3 e·MMC Communication Interface 6.4 Bus Protocol. 6.5 Bus Speed Modes.                                                                                                                     | 13<br>14<br>14             |

| 7. | E-MMC FUNCTIONAL DESCRIPTION                                                                                                                                                                                                        | 16                         |

|    | 7.1 E·MMC OVERVIEW 7.2 BOOT OPERATION MODE 7.3 DEVICE IDENTIFICATION MODE. 7.4 INTERRUPT MODE. 7.5 DATA TRANSFER MODE 7.6 INACTIVE MODE 7.7 H/W RESET OPERATION 7.8 NOISE FILTERING TIMING FOR H/W RESET                            | 16<br>16<br>16<br>16<br>16 |

| 8. | THE E-MMC BUS                                                                                                                                                                                                                       | 18                         |

|    | 8.1 POWER-UP 8.2 BUS OPERATING CONDITIONS 8.3 BUS SIGNAL LEVELS 8.4 BUS TIMING 8.5 BUS TIMING FOR DAT SIGNALS DURING DUAL DATA RATE OPERATION 8.6 BUS TIMING SPECIFICATION IN HS200 MODE 8.7 BUS TIMING SPECIFICATION IN HS400 MODE | 2C<br>23<br>24<br>27<br>28 |

| 9. | E·MMC REGISTERS                                                                                                                                                                                                                     | 34                         |

|    | 9.1 OCR REGISTER. 9.2 CID REGISTER. 9.3 CSD REGISTER 9.4 EXTENDED CSD REGISTER 9.5 RCA REGISTER                                                                                                                                     | 35<br>35                   |

|    | DARTAWANER CACTELA                                                                                                                                                                                                                  | 44                         |

# ASFC 3D pSLC Series – Industrial embedded MMC 5.1 5 GBytes and 10 GBytes

# 1. ProductSummary

- Capacities: 5GBytes & 10 GBytes

- OperatingTemperatureRange1:

- o Industrial Operating Temperature -40 to 85°C

# 2. ProductFeatures

- Fully compliant with JEDEC e·MMC 5.1 Standard (JESD84-B51)

- 153-ball BGA, 0.5mm pitch, 11.5 x 13mm, RoHS compliant

- 3D TLC NAND base technology in Enhanced Mode (pSLC)

- High performance e·MMC 5.1 specification

- o Eleven-wire bus (clock, Data Strobe, 1 bit command, 8 bit data bus) and a hardware reset

- Three different data bus width modes: 1-bit (default), 4-bit, and 8-bit

- Clock frequencies o-200MHz, High Speed Mode HS400

- o Command Queue Feature according to e∙MMC Spec 5.1

- Up to 330MB/s sequential read and up to 250MB/s sequential write

- Power Supply: (Low-power CMOS technology)

- o VCCQ 1.7V to 1.95V or 2.7V to 3.6V e·MMC supply / VCC 2.7V to 3.6V NAND Flash supply

- Optimized FW algorithms

- o Power-fail data loss protection

critical levels have occurred

- Wear Leveling technology

- Equal wear leveling of static and dynamic data. The wear leveling assures that dynamic data as well as static data is balanced evenly across the memory. With that the maximum write endurance of the device is ensured

- Read Disturb Management

The read commands per region are monitored and the content is conditionally refreshed when

- Auto Read Refresh

- The interruptible background process maintains the user data for Read Disturb effects or Retention degradation due to high temperature effects

- o Diagnostic features with Device Health Report according to e·MMC Spec 5.1, and detailed Lifetime Monitor data (Alliance proprietary, accessible through standard e·MMC commands).

- o Field Firmware update<sup>2</sup> according to e⋅MMC Spec 5.1

- o Discard and Sanitize, Trim

- o Boot Operation Mode and Alternative Boot Operation Mode

- Replay Protected Memory Block (RPMB)

#### Note:

- <sup>1</sup> Adequate airflow is required to ensure the temperature does not exceed 85°C (industrial temperature drive)

- <sup>2</sup> The support of In-Field FW update capabilities on host systems is recommended.

Confidential -3 / 44- Rev.1.0 May 2024

# 3. Ordering Information

**Table 1. Ordering Information**

| Capacities (GB) | Part Number       | eMMC<br>Version | NAND<br>Die | Temperature                      | Package Size<br>(mm) | Package<br>Type |

|-----------------|-------------------|-----------------|-------------|----------------------------------|----------------------|-----------------|

| 5GB             | ASFC5G31P3-51BIN  | 5.1             | 128Gb x 1   | Industrial Grade<br>-40°C ~ 85°C | 11.5x13.0x1.0        | 153ball<br>FBGA |

| 10GB            | ASFC10G31P3-51BIN | 5.1             | 256Gb x 1   | Industrial Grade -40°C ~ 85°C    | 11.5x13.0x1.0        | 153ball<br>FBGA |

# 4. Product Description

The Alliance e·MMC is a managed non-volatile storage consisting of a single chip MMC controller and a NAND flash memory chip inside a JEDEC defined standard BGA package. It is specially designed as a small form factor memory product for storage of data and as a boot media. The performance is optimized to a mostly read operation mode at low power consumption. The utilization of 3D pSLC NAND technology targets higher demanding and write intensive industrial applications, which is supported by the industrial temperature grade specification.

The e·MMC controller directly manages NAND flash, including ECC, wear-leveling, IOPS optimization and read sensing. The 3D pSLC firmware features support high throughput for large data transfers and performance for small random data more commonly found in code usage. It also contains several security features as well as multiple boot partitions. Uses advanced refresh features for retention optimization for read intensive applications.

e·MMC communication is based on an advanced 11-signal bus. The communication protocol is defined as a part of the JEDEC e·MMC standard and referred to as the e·MMC mode.

Confidential -4 / 44- Rev.1.0 May 2024

# **4.1 Performance Specifications**

The read/write sequential and random CDM performance benchmarks are detailed in Table 2.

Table 2: Read/Write Performance

| abic E. Read                                                                  | ie 2. Redd/Write Ferrormance                                                  |                                     |                                     |                                      |                                      |                       |  |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------|-------------------------------------|--------------------------------------|--------------------------------------|-----------------------|--|

|                                                                               | ASFC5G31P3-51BIN                                                              |                                     |                                     |                                      |                                      |                       |  |

| Capacity Max. Sequential Read Max. Sequential Write HS400 (MBPS) HS400 (MBPS) |                                                                               | Max. Random Read 4K<br>HS400 (IOPS) |                                     | Max. Random Write 4K<br>HS400 (IOPS) |                                      |                       |  |

|                                                                               | measuring tool CDM                                                            | measuring tool CDM                  | Proprietary<br>tool <sup>3</sup>    | measuring<br>tool CDM                | Proprietary<br>tool <sup>3</sup>     | measuring<br>tool CDM |  |

| 5 GBytes                                                                      | 270                                                                           | 120                                 | 17,500                              | 4,200                                | 17,500                               | 2000                  |  |

| Capacity                                                                      | Capacity Max. Sequential Read Max. Sequential Write HS200 (MBPS) HS200 (MBPS) |                                     | Max. Random Read 4K<br>HS200 (IOPS) |                                      | Max. Random Write 4K<br>HS200 (IOPS) |                       |  |

|                                                                               | measuring tool CDM                                                            | measuring tool CDM                  | Proprietary<br>tool <sup>3</sup>    | measuring<br>tool CDM                | Proprietary<br>tool <sup>3</sup>     | measuring<br>tool CDM |  |

| 5 GBytes                                                                      | 180                                                                           | 95                                  | 17,500                              | n.a                                  | 17,500                               | n.a                   |  |

Table 3: Read/Write Performance

|                                                                                     | ASFC10G31P3-51BIN                    |                                       |                                           |                                      |                                  |                                      |  |

|-------------------------------------------------------------------------------------|--------------------------------------|---------------------------------------|-------------------------------------------|--------------------------------------|----------------------------------|--------------------------------------|--|

| Capacity                                                                            | Max. Sequential Read<br>HS400 (MBPS) | Max. Sequential Write<br>HS400 (MBPS) | ite Max. Random Read 4K M<br>HS400 (IOPS) |                                      |                                  | Max. Random Write 4K<br>HS400 (IOPS) |  |

|                                                                                     | measuring tool CDM                   | measuring tool CDM                    | Proprietary<br>tool <sup>3</sup>          | measuring<br>tool CDM                | Proprietary<br>tool³             | measuring<br>tool CDM                |  |

| 10 GBytes                                                                           | 280                                  | 120                                   | 17,500                                    | 4,300                                | 20,500                           | 2,050                                |  |

| Capacity Max. Sequential Read Max. Sequential Write Ma<br>HS200 (MBPS) HS200 (MBPS) |                                      | Max. Random Read 4K<br>HS200 (IOPS)   |                                           | Max. Random Write 4K<br>HS200 (IOPS) |                                  |                                      |  |

|                                                                                     | measuring tool CDM                   | measuring tool CDM                    | Proprietary<br>tool <sup>3</sup>          | measuring<br>tool CDM                | Proprietary<br>tool <sup>3</sup> | measuring<br>tool CDM                |  |

| 10 GBytes                                                                           | 180                                  | 115                                   | 17,500                                    | n.a                                  | 20,000                           | n.a                                  |  |

Please note that Gen3 Flash variants were measured with Crystal Disk Mark x64 5x 1GiB (CDM 7.0.0) only

#### Note:

3. Controller supplier proprietary reader board: measuring without OS

Confidential -5 / 44- Rev.1.0 May 2024

# 4.2 Current Consumption

The drive-level current consumption as a function of operating mode is shown in Table 4.

**Table 4: Current Consumption**

| ASFC5G31P3-51BIN/ASFC10G31P3-51BIN |                       |                      |                       |                      |                       |                      |       |

|------------------------------------|-----------------------|----------------------|-----------------------|----------------------|-----------------------|----------------------|-------|

| Canadity                           | Typ. Rea              | d Current            | Typ. Writ             | e Current            | Typ. Slee             | p Current            | llm:t |

| Capacity                           | V <sub>CCQ</sub> 1.8V | V <sub>CC</sub> 3.3V | V <sub>CCQ</sub> 1.8V | V <sub>CC</sub> 3.3V | V <sub>ccQ</sub> 1.8V | V <sub>CC</sub> 3.3V | Unit  |

| 5 GBytes                           | 131                   | 77                   | 89                    | 43                   | 0.06                  | 0.02                 | mA    |

| 10 GBytes                          | 132                   | 77                   | 89                    | 40                   | 0.06                  | 0.02                 |       |

Values given for an 8-bit bus width, a clock frequency of 200MHz DDR mode, V<sub>CC</sub> = 3.3V±5%, V<sub>CCQ</sub>=1.8V±5%

# 4.3 Environmental Specifications

## 4.3.1 Recommended Operating Conditions

The recommended operating conditions are provided in Table 5.

Table 5: Recommended Operating Conditions<sup>4</sup>

| Parameter                             | Value                 |  |  |

|---------------------------------------|-----------------------|--|--|

| Industrial Operating Temperature      | -40°C to 85°C         |  |  |

| Power Supply V <sub>CC</sub> Voltage  | 2.7-3.6V              |  |  |

| Power Supply V <sub>CCQ</sub> Voltage | 1.7-1.95V or 2.7-3.6V |  |  |

## 4.3.2 Recommended Storage Conditions

The recommended storage conditions are listed in Table 6.

Table 6: Recommended Storage Conditions

| Parameter                      | Value         |

|--------------------------------|---------------|

| Industrial Storage Temperature | -40°C to 85°C |

#### Note:

4. Adequate airflow is required to ensure the temperature does not exceed 85°C (industrial temperature drive)

Confidential -6 / 44- Rev.1.0 May 2024

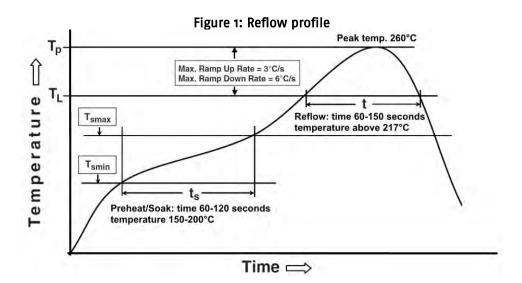

# 4.3.3 Reflow profile and MSL

#### Table 7: Reflow and MSL conditions

| Parameter | Condition                                                                               |  |

|-----------|-----------------------------------------------------------------------------------------|--|

| MSL       | Level 3 (storage condition 168 hours, ≦30°C/ 60% RH)                                    |  |

| Reflow    | According to IPC/JEDEC J-STD-020D.1:<br>Peak temp 260°C, 217°C endurance 60~150 seconds |  |

# 4.3.4 EMC

# Table 8: EMC / EMI

| Parameter | Value                                                                  |  |  |

|-----------|------------------------------------------------------------------------|--|--|

| FMC / FMI | Human Body Model: up to ±2 kV according to MIL-STD-883G, Method 3015.7 |  |  |

| EMC / EMI | Charged Device Model: up to ±500 V according to JESD22-C101            |  |  |

Confidential -7 / 44- Rev.1.0 May 2024

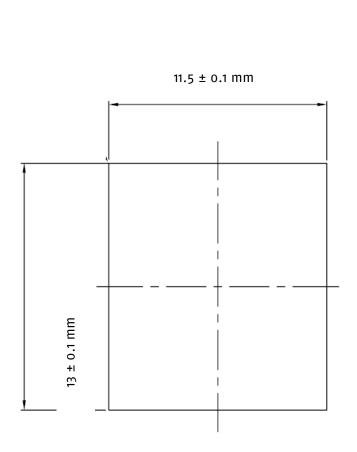

# 4.4 Mechanical Specifications

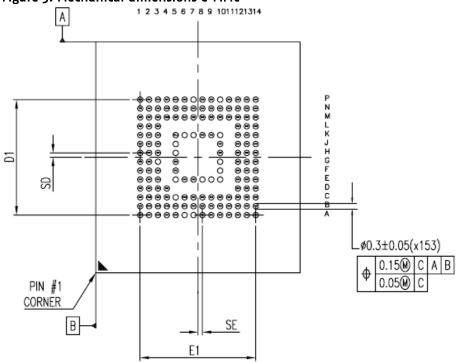

Physical dimensions are detailed in Table 9. Also refer to Figure 2.

Table 9: Physical Dimensions

| Physical Dimensions   |          |    |

|-----------------------|----------|----|

| Length                | 13±0.1   |    |

| Width                 | 11.5±0.1 | mm |

| Thickness (Max)       | 1.2 max. |    |

| Weight (Max Capacity) | < 1g     | g  |

# 4.5 Reliability and Endurance

Data retention at the beginning and end of life is provided in following Table 10.

**Table 10: Reliability**

| Parameter <sup>5</sup>                            | Value    |

|---------------------------------------------------|----------|

| Data Retention at beginning @ 40°C                | 10 years |

| Data Retention at life end (30k PE cycles) @ 40°C | 1 year   |

Endurance represented as both TeraBytes Written (TBW) and full Drive Writes Per Day (DWPD) is provided as maximum values in the following Table 11.

Table 11: Endurance<sup>6</sup>

| ASFC5G31P3-51BIN/ASFC10G31P3-51BIN |                |                   |  |  |  |  |  |

|------------------------------------|----------------|-------------------|--|--|--|--|--|

|                                    | Max. Endurance |                   |  |  |  |  |  |

| Capacity                           | TBW            | DWPD <sup>7</sup> |  |  |  |  |  |

| 5 GBytes                           | 168            | 29.7              |  |  |  |  |  |

| 10 GBytes                          | 330            | 29.2              |  |  |  |  |  |

#### Note:

Confidential -8 / 44- Rev.1.0 May 2024

<sup>5.</sup>NAND Flash data retention and endurance characteristics are defined according to JEDEC JESD47 and JESD22. The endurance limits of the storage shall be monitored by the life time information and simulated before field usage by the customer.

<sup>6.</sup>According to JEDEC (JESD47I), the time to write the full TBW is a minimum of 18 months. Higher average daily data volume reduces the specified TBW. The values listed are estimates and are subject to change without notice.

<sup>7.</sup>DWPD values are based on a service life of 3 years

# 4.6 Drive Geometry Specification

The user capacities are shown in following Table 12.

Table 12: Drive Geometry

| Paw Canacity | User Capacity Total LBA |            | User Addressable Bytes |  |

|--------------|-------------------------|------------|------------------------|--|

| Raw Capacity | user capacity           | Decimal    | (Unformatted)          |  |

| 16 GBytes    | 5 GBytes                | 10,059,776 | 5,150,605,312          |  |

| 32 GBytes    | 10 GBytes               | 20,135,936 | 10,309,599,232         |  |

Table 13: Partition capacity specification

| Capacity       | Boot partition 1 | Boot partition 2 | RPMB    |

|----------------|------------------|------------------|---------|

| 5 to 10 GBytes | 32,256KB         | 32,256KB         | 4,096KB |

Confidential -9 / 44- Rev.1.0 May 2024

# 5. Package Mechanical

# 5.1 Physical description

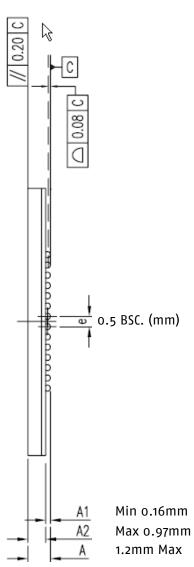

The e·MMC contains a single chip controller and Flash memory module(s). The controller interfaces with a host system allowing data to be written to and read from the Flash memory module(s). Figure 2 and Figure 3 show card dimensions.

Figure 2: Mechanical dimensions e·MMC

Package Mechanical (11.5 x 13.0 x 1.2mm)

Confidential -10 / 44- Rev.1.0 May 2024

# BOTTOM VIEW

| N   | SE (MM)   | SD (MM)   | E1(MM)    | D1(MM)    | JEDEC(REF) |

|-----|-----------|-----------|-----------|-----------|------------|

| 153 | 0.25 BSC. | 0.25 BSC. | 6.50 BSC. | 6.50 BSC. | MO-276 BA  |

Confidential -11 / 44- Rev.1.0 May 2024

# 6. e·MMC device and system

# 6.1 e·MMC system overview

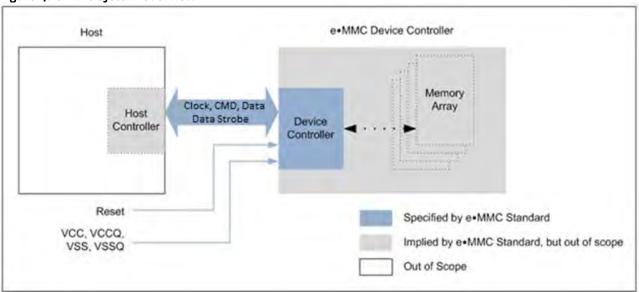

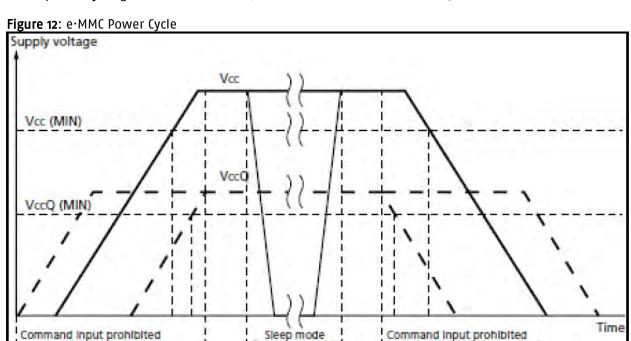

The e·MMC specification covers the behavior of the interface and the Device controller. As part of this specification the existence of a host controller and a memory storage array are implied but the operation of these pieces is not fully specified.

Figure 4: e·MMC System Overview

Confidential -12 / 44- Rev.1.0 May 2024

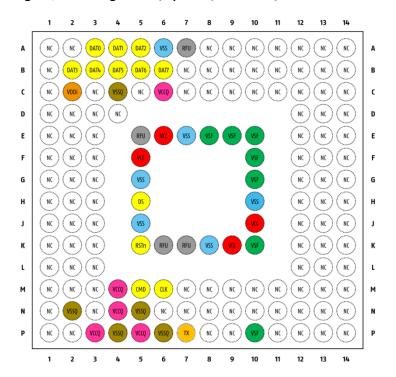

## 6.2 Pinout

## Figure 5: Ball assignment (top view, ball down)

Table 14: Pinout

| Name  | Type¹     | Ball No.                | Description                                                                                                                                                                                     |  |  |  |  |

|-------|-----------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CLK   | ı         | M6                      | Clock:<br>Each cycle directs a 1-bit transfer on the command and DAT lines.                                                                                                                     |  |  |  |  |

| CMD   | I/O/PP/OD | M5                      | Command: A bidirectional channel used for device initialization an command transfer. Command has two operating modes: 1) Open-drain for initialization. 2) Push-pull for fast command transfer. |  |  |  |  |

| DATo  | I/O/PP    | A3                      | Data I/Oo: Bidirectional channel used for data transfer.                                                                                                                                        |  |  |  |  |

| DAT1  | I/O/PP    | A4                      | Data I/01: Bidirectional channel used for data transfer.                                                                                                                                        |  |  |  |  |

| DAT2  | I/O/PP    | A5                      | Data I/O2: Bidirectional channel used for data transfer.                                                                                                                                        |  |  |  |  |

| DAT3  | I/O/PP    | B2                      | Data I/03: Bidirectional channel used for data transfer.                                                                                                                                        |  |  |  |  |

| DAT4  | I/O/PP    | В3                      | Data I/O4: Bidirectional channel used for data transfer.                                                                                                                                        |  |  |  |  |

| DAT5  | I/O/PP    | B4                      | Data I/05: Bidirectional channel used for data transfer.                                                                                                                                        |  |  |  |  |

| DAT6  | I/O/PP    | B5                      | Data I/06: Bidirectional channel used for data transfer.                                                                                                                                        |  |  |  |  |

| DAT7  | I/O/PP    | B6                      | Data I/07: Bidirectional channel used for data transfer.                                                                                                                                        |  |  |  |  |

| RST_n | I         | К5                      | Reset signal pin                                                                                                                                                                                |  |  |  |  |

| VCC   | S         | E6, F5, J10, K9         | VCC: Flash memory I/F and Flash memory power supply.                                                                                                                                            |  |  |  |  |

| vccq  | S         | C6, M4, N4, P3, P5      | VCCQ : Memory controller core and MMC interface I/O power supply.                                                                                                                               |  |  |  |  |

| VSS   | S         | A6, E7, G5, H10, J5, K8 | VSS: Flash memory I/F and Flash memory ground connection.                                                                                                                                       |  |  |  |  |

| VSSQ  | S         | C4, N2, N5, P4, P6      | VSSQ: Memory controller core and MMC I/F ground connection.                                                                                                                                     |  |  |  |  |

| VDDi  |           | C2                      | VDDi : Connect capacitor Creg from VDDi to GND.                                                                                                                                                 |  |  |  |  |

| DS    | O/PP      | H5                      | Data Strobe: Newly assigned pin for HS400 mode.                                                                                                                                                 |  |  |  |  |

| NC    |           |                         | Not connected                                                                                                                                                                                   |  |  |  |  |

<sup>1.</sup> I: input; O: output; PP: push-pull; OD: open-drain; NC: Not connected; S: power supply.

Confidential -13 / 44- Rev.1.0 May 2024

# 6.3 e MMC Communication Interface

The e·MMC device transfers data via a configurable number of data bus signals. The communication signals are:

#### Clock (CLK)

Each cycle of this signal directs a one bit transfer on the command and either a one bit (1x) or a two bits transfer (2x) on all the data lines. The frequency may vary between zero and the maximum clock frequency.

#### Data Strobe (DS)

This signal is generated by the device and used for output in HS400 mode. The frequency of this signal follows the frequency of CLK. For data output each cycle of this signal directs two bits transfer(2x) on the data – one bit for positive edge and the other bit for negative edge. For CRC status response output and CMD response output (enabled only HS400 enhanced strobe mode), the CRC status is latched on the positive edge only, and don't care on the negative edge.

#### Command (CMD)

This signal is a bidirectional command channel used for Device initialization and transfer of commands. The CMD signal has two operation modes: open-drain for initialization mode, and push-pull for fast command transfer. Commands are sent from the e·MMC host controller to the e·MMC Device and responses are sent from the Device to the host.

#### Input/Outputs (DATo-DAT7)

These are bidirectional data channels. The DAT signals operate in push-pull mode. Only the Device or the host is driving these signals at a time. By default, after power up or reset, only DATo is used for data transfer. A wider data bus can be configured for data transfer, using either DATo-DAT3 or DATo-DAT7, by the e·MMC host controller. The e·MMC Device includes internal pull-ups for data lines DAT1-DAT7.

Immediately after entering the 4-bit mode, the Device disconnects the internal pull ups of lines DAT1, DAT2, and DAT3. Correspondingly, immediately after entering to the 8-bit mode the Device disconnects the internal pull-ups of lines DAT1-DAT7.

#### 6.4 Bus Protocol

After a power-on reset, the host must initialize the device by a special message-based e·MMC bus protocol. For more details, refer to section 5.3.1 of the JEDEC Standard JESD84-B51.

#### 6.5 Bus Speed Modes

e·MMC defines several bus speed modes as shown in following Table 15.

Table 15: Bus Speed Mode

| Mode Name                                          | Data Rate | IO Voltage | Bus Width | Frequency | Max Data Transfer<br>(implies x8 bus<br>width) |

|----------------------------------------------------|-----------|------------|-----------|-----------|------------------------------------------------|

| Backwards<br>Compatibility with<br>legacy MMC card | Single    | 3.3/1.8V   | 1, 4, 8   | 0-26MHz   | 26MB/s                                         |

| High Speed SDR                                     | Single    | 3.3/1.8V   | 4, 8      | 0-52MHz   | 52MB/s                                         |

| High Speed DDR                                     | Dual      | 3.3/1.8V   | 4, 8      | o-52MHz   | 104MB/s                                        |

| HS200                                              | Single    | 1.8V       | 4, 8      | 0-200MHz  | 200MB/s                                        |

| HS400                                              | Dual      | 1.8V       | 8         | 0-200MHz  | 400MB/s                                        |

#### 6.5.1 HS200 Bus Speed Mode

The HS200 mode offers the following features:

- SDR Data sampling method

- CLK frequency up to 200MHz Data rate up to 200MB/s

- 8-bits bus width supported

- Single ended signaling with 4 selectable Drive Strength

- Signaling levels of 1.8V

- Tuning concept for Read Operations

Confidential -14 / 44- Rev.1.0 May 2024

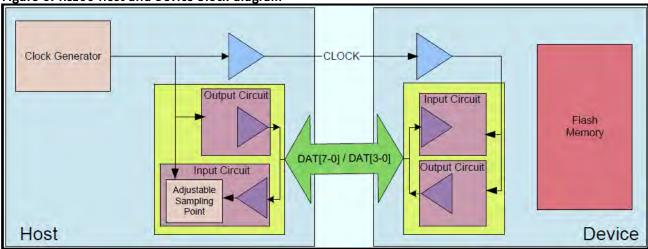

#### 6.5.2 HS200 System Block Diagram

Figure 6 shows a typical HS200 Host and Device system. The host has a clock generator, which supplies CLK to the Device. For write operations, clock and data direction are the same, write data can be transferred synchronous with CLK, regardless of transmission line delay. For read operations, clock and data direction are opposite; the read data received by Host is delayed by round-trip delay, output delay and latency of Host and Device. For reads, the Host needs to have an adjustable sampling point to reliably receive the incoming data.

Figure 6: HS200 Host and Device block diagram

# 6.5.3 HS400 Bus Speed mode

The HS400 mode has the following features:

- DDR Data sampling method

- CLK frequency up to 200MHz, Data rate is up to 400MB/s

- Only 8-bit bus width supported

- Signaling levels of 1.8V

- Support up to 5 selective Drive Strength

- Data strobe signal is toggled only for Data out and CRC response

# 6.5.4 HS400 System Block Diagram

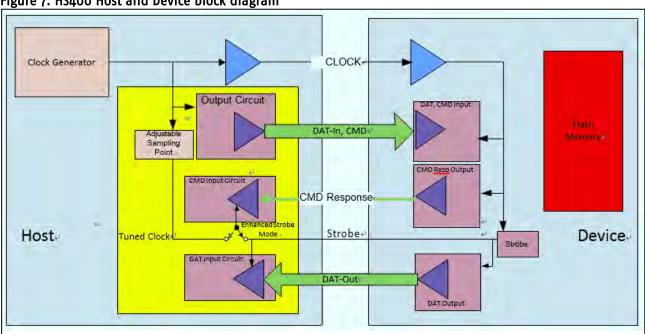

Figure 7 shows a typical HS400 Host and Device system. The host has a clock generator, which supplies CLK to the Device. For read operations, Data Strobe is generated by device output circuit. Host receives the data which is aligned to the edge of Data Strobe.

Figure 7: HS400 Host and Device block diagram

# 7. e·MMC Functional Description

#### 7.1 e·MMC Overview

All communication between host and device are controlled by the host (master). The host sends a command, which results in a device response. For more details, refer to section 6.1 of the JEDEC Standard JESD84-B51. Five operation modes are defined for the e·MMC system:

- Boot operation mode

- Device identification mode

- Interrupt mode

- Data transfer mode

- Inactive mode

# 7.2 Boot Operation Mode

In boot operation mode, the master (e·MMC host) can read boot data from the slave (e·MMC device) by keeping CMD line low or sending CMDo with argument + oxFFFFFFFA, before issuing CMD1. The data can be read from either boot area or user area depending on register setting. For more details, refer to section 6.3 of the JEDEC Standard JESD84-B51.

## 7.3 Device Identification Mode

While in device identification mode the host resets the device, validates operation voltage range and access mode, identifies the device and assigns a Relative device Address (RCA) to the device on the bus. All data communication in the Device Identification Mode uses the command line (CMD) only. For more details, refer to section 6.4 of the JEDEC Standard JESD84-B51.

## 7.4 Interrupt Mode

The interrupt mode on the e·MMC system enables the master (e·MMC host) to grant the transmission allowance to the slaves (Device) simultaneously. This mode reduces the polling load for the host and hence, the power consumption of the system, while maintaining adequate responsiveness of the host to a Device request for service. Supporting e·MMC interrupt mode is an option, both for the host and the Device. For more details, refer to section 6.5 of the JEDEC Standard JESD84-B51.

#### 7.5 Data Transfer Mode

When the Device is in *Stand-by* State, communication over the CMD and DAT lines will be performed in push-pull mode. For more details, refer to section 6.6 of the JEDEC Standard JESD84-B51.

#### 7.6 Inactive Mode

The device will enter inactive mode if either the device operating voltage range or access mode is not valid. The device can also enter inactive mode with GO\_INACTIVE\_STATE command (CMD15). The device will reset to *Pre-idle* state with power cycle. For more details, refer to section 6.1 of the JEDEC Standard JESD84-B51.

Confidential -16 / 44- Rev.1.0 May 2024

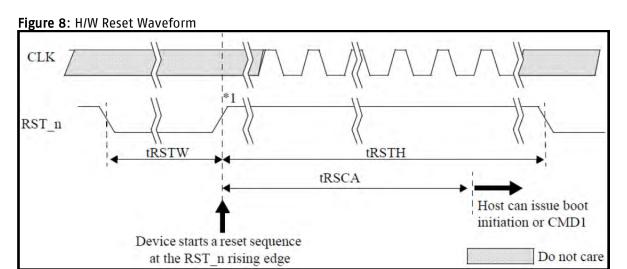

# 7.7 H/W Reset Operation

1. Device will detect the rising edge of RST\_n signal to trigger internal reset sequence

Table 16: H/W Reset Timing Parameters

| Symbol | Comment                           | Min. | Max. | Unit |

|--------|-----------------------------------|------|------|------|

| tRSTW  | RST_n pulse width                 | 1    |      | [us] |

| tRSCA  | RST_n to Command time             | 200¹ |      | [us] |

| tRSTH  | RST_n high period (interval time) | 1    |      | [us] |

<sup>1. 74</sup> cycles of clock signal required before issuing CMD1 or CMD0 with argument oxFFFFFFFA

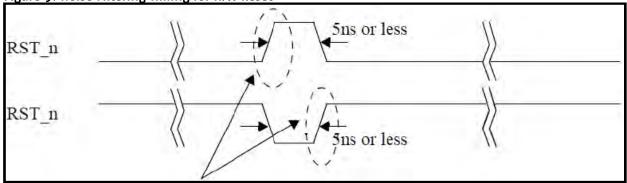

# 7.8 Noise Filtering Timing for H/W Reset

Device must filter out 5ns or less pulse width for noise immunity

Figure 9: Noise Filtering Timing for H/W Reset

Device must not detect these rising edge.

Device must not detect 5ns or less of positive or negative RST\_n pulse. Device must detect more than or equal to 1us of positive or negative RST\_n pulse width.

Confidential -17 / 44- Rev.1.0 May 2024

# 8. The e-MMC bus

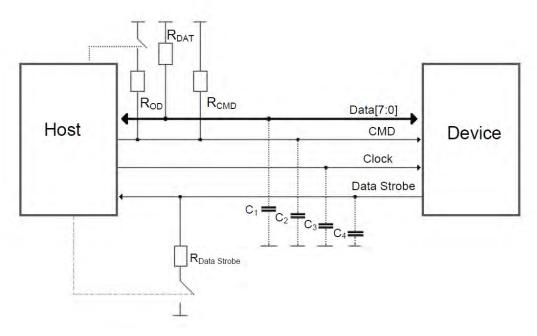

The e·MMC bus has eleven communication lines and three supply lines:

- CMD: Command is a bidirectional signal. The host and Device drivers are operating in two modes, open drain and push/pull.

- DATo-7: Data lines are bidirectional signals. Host and Device drivers are operating in push-pull mode.

- CLK: Clock is a host to Device signal. CLK operates in push-pull mode.

- Data Strobe: Data Strobe is a Device to host signal. Data Strobe operates in push-pull mode.

Figure 10: Bus Circuitry Diagram

The  $R_{\text{OD}}$  is switched on and off by the host synchronously to the open-drain and push-pull mode transitions. The host does not have to have open drain drivers, but must recognize this mode to switch on the  $R_{\text{OD}}$ .  $R_{\text{DAT}}$  and  $R_{\text{CMD}}$  are pull-up resistors protecting the CMD and the DAT lines against bus floating device when all device drivers are in a high-impedance mode.

A constant current source can replace the  $R_{DD}$  by achieving a better performance (constant slopes for the signal rising and falling edges). If the host does not allow the switchable  $R_{DD}$  implementation, a fixed  $R_{CMD}$  can be used). Consequently the maximum operating frequency in the open drain mode has to be reduced if the used  $R_{CMD}$  value is higher than the minimal one given in.

$R_{Data\ strobe}$  is pull-down resistor used in HS400 device.

Confidential -18 / 44- Rev.1.0 May 2024

### 8.1 Power-up

## 8.1.1 e·MMC power-up

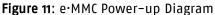

An e·MMC bus power-up is handled locally in each device and in the bus master. Figure 11 shows the power-up sequence and is followed by specific instructions regarding the power-up sequence. Refer to section 10.1 of the JEDEC Standard JESD84-B51.

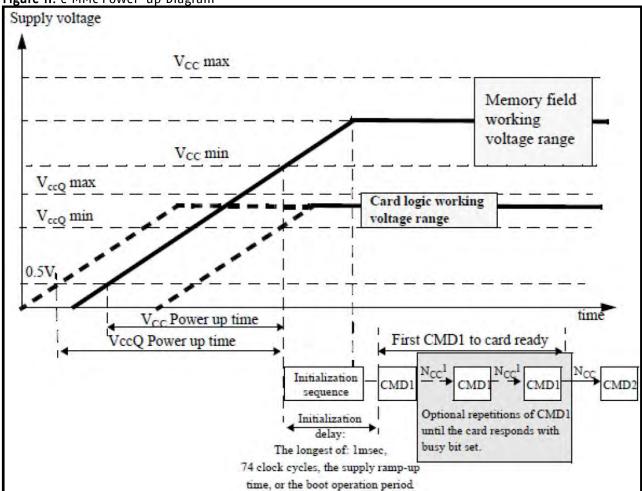

#### 8.1.2 e·MMC Power Cycling

The master can execute any sequence of  $V_{CCQ}$  and  $V_{CCQ}$  power-up/power-down. However, the master must not issue any commands until  $V_{CC}$  and  $V_{CCQ}$  are stable within each operating voltage range. After the slave enters sleep mode, the master can power-down  $V_{CC}$  to reduce power consumption. It is necessary for the slave to be ramped up to  $V_{CC}$  before the host issues CMD5 (SLEEP\_AWAKE) to wake the slave unit. For more information about power cycling refer to Section 10.1.3 of the JEDEC Standard JESD84-B51.

# 8.2 Bus Operating Conditions

**Table 17: General Operating Conditions**

| Parameter                                                                                              | Symbol | Min. | Max.                      | Unit | Remark |

|--------------------------------------------------------------------------------------------------------|--------|------|---------------------------|------|--------|

| Peak voltage on all lines                                                                              |        | -0.5 | V <sub>CCQ</sub> +<br>0.5 | V    |        |

| All Inputs                                                                                             |        |      |                           |      |        |

| Input Leakage Current (before initialization sequence and/or the internal pull up resistors connected) |        | -100 | 100                       | μΑ   |        |

| Input Leakage Current (after initialization sequence and the internal pull up resistors disconnected)  |        | -2   | 2                         | μΑ   |        |

| All Outputs                                                                                            |        |      |                           |      |        |

| Output Leakage Current (before initialization sequence)                                                |        | -100 | 100                       | μΑ   |        |

| Output Leakage Current (after initialization sequence)                                                 |        | -2   | 2                         | μA   |        |

Confidential -20 / 44- Rev.1.0 May 2024

#### 8.2.1 Power supply e·MMC

In the e·MMC,  $V_{CC}$  is used for the NAND flash device and its interface voltage;  $V_{CCQ}$  is for the controller and the MMC interface voltage as shown in Figure 13. The core regulator is optional and only required when internal core logic voltage is regulated from  $V_{CCQ}$ . A  $C_{Reg}$  capacitor must be connected to the  $V_{DDi}$  terminal to stabilize regulator output on the system.

Figure 13: e⋅MMC Internal Power Diagram

## 8.2.2 e·MMC Power Supply Voltages

The e·MMC supports one or more combinations of  $V_{cc}$  and  $V_{ccQ}$  as shown in Table 18. The  $V_{ccQ}$  must be defined at equal to or less than  $V_{cc}$ .

Table 18: e-MMC Operating Voltage

| Parameter                | Symbol            | Min. | Max. | Unit | Remarks |

|--------------------------|-------------------|------|------|------|---------|

| Supply voltage (NAND)    | V <sub>CC</sub>   | 2.7  | 3.6  | V    |         |

| Supply voltage (1/0)     | V                 | 2.7  | 3.6  | V    |         |

| Supply voltage (I/O)     | V <sub>ccQ</sub>  | 1.7  | 1.95 | V    |         |

| Supply power-up for 3.3V | t <sub>PRUH</sub> |      | 35   | ms   |         |

| Supply power-up for 1.8V | t <sub>PRUL</sub> |      | 25   | ms   |         |

The e·MMC must support at least one of the valid voltage configurations, and can optionally support all valid voltage configurations (see Table 19).

Table 19: e·MMC Voltage Combinations

|     |           | Vccq       |            |  |

|-----|-----------|------------|------------|--|

|     |           | 1.7V−1.95V | 2.7V-3.6V° |  |

| Vcc | 2.7V-3.6V | Valid      | Valid      |  |

<sup>\*</sup> VCCQ (I/O) 3.3 volt range is not supported in HS200 /HS400 devices

# 8.2.3 Bus Signal Line Load

The total capacitance  $C_L$  of each line of the e·MMC bus is the sum of the bus master capacitance  $C_{HOST}$ , the bus capacitance  $C_{BUS}$  itself and the capacitance  $C_{DEVICE}$  of e·MMC connected to this line:

$$C_L = C_{HOST} + C_{BUS} + C_{DEVICE}$$

The sum of the host and bus capacitances must be under 20pF.

Table 20: Signal Line Load

| Parameter                                | Symbol                      | Min.  | Max.    | Unit | Remark                                                                                                                                                            |

|------------------------------------------|-----------------------------|-------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pull-up resistance for CMD               | $R_{\text{CMD}}$            | 4.7   | 50      | Kohm | to prevent bus floating                                                                                                                                           |

| Pull-up resistance for DATo-7            | $R_{\text{DAT}}$            | 10    | 50      | Kohm | to prevent bus floating                                                                                                                                           |

| Pull-up resistance for RST_n             | R <sub>RST_n</sub>          | 4.7   | 50      | Kohm | It is not necessary to put pull-up resistance on RST_n (H/W rest) line if host does not use H/W reset. (Extended CSD register [162] = 0 b)                        |

| Bus signal line capacitance              | CL                          |       | 30      | pF   | Single Device                                                                                                                                                     |

| Single Device capacitance                | $C_{BGA}$                   |       | 6       | pF   |                                                                                                                                                                   |

| Maximum signal line inductance           |                             |       | 16      | nH   |                                                                                                                                                                   |

| Impedance on CLK / CMD<br>/ DATo~7       |                             | 45    | 55      | ohm  | Impedance match                                                                                                                                                   |

| Serial's resistance on CLK<br>line       | SR <sub>CLK</sub>           | 0     | 47      | ohm  |                                                                                                                                                                   |

| Serial's resistance on CMD / DATo~7 line | $SR_{CMD} SR_{DATo \sim 7}$ | 0     | 47      | ohm  |                                                                                                                                                                   |

| V descupling capacitor                   | C <sub>VCCQ</sub> 1         | 4.7   | 10      | μF   | It should be located as close as possible to the balls defined in order to minimize                                                                               |

| V <sub>CCQ</sub> decoupling capacitor    | C <sub>VCCQ</sub> 2         | 0.1   | 0.1     | μг   | connection parasitic                                                                                                                                              |

| V canacitor value                        | C <sub>VCC</sub> 1          | 4.7   | 10      | E    | It should be located as close as possible to the balls defined in order to minimize                                                                               |

| V <sub>CC</sub> capacitor value          | C <sub>VCC</sub> 2          | 0.1   | 0.1     | μF   | connection parasitic                                                                                                                                              |

| V <sub>DDi</sub> capacitor value         | $C_{REG}$                   | 1+0.1 | 2.2+0.1 | μF   | To stabilize regulator output to controller core logics. It should be located as close as possible to the balls defined in order to minimize connection parasitic |

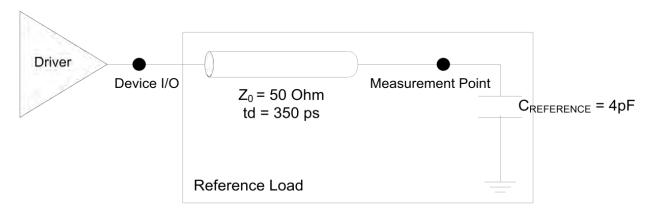

#### 8.2.4 HS400 reference load

The circuit in Figure 14 shows the reference load used to define the HS400 Device Output Timings and overshoot / undershoot parameters.

The reference load is made up by the transmission line and the CREFERENCE capacitance.

The reference load is not intended to be a precise representation of the typical system environment nor a depiction of the actual load presented by a production tester.

System designers should use IBIS or other simulation tools to correlate the reference load to system environment. Manufacturers should correlate to their production test conditions.

Delay time (td) of the transmission line has been introduced to make the reference load independent from the PCB technology and trace length.

Figure 14: HS400 reference load

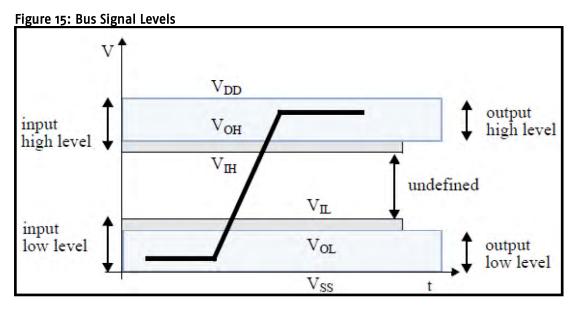

# 8.3 Bus Signal Levels

As the bus can be supplied with a variable supply voltage, all signal levels are related to the supply voltage.

# 8.3.1 Open-drain Mode Bus Signal Level

Table 21: Open-drain Bus Signal Level

| Parameter           | Symbol | Min.      | Max. | Unit | Conditions    |

|---------------------|--------|-----------|------|------|---------------|

| Output HIGH voltage | VOH    | VDD - 0.2 |      | V    | IOH = -100 μA |

| Output LOW voltage  | VOL    |           | 0.3  | V    | IOL = 2 mA    |

The input levels are identical with the push-pull mode bus signal levels.

#### 8.3.2 Push-pull mode bus signal level— e·MMC

The device input and output voltages shall be within the following specified ranges for any VDD of the allowed voltage range

For 2.7V-3.6V  $V_{CCQ}$  range (compatible with JESD8C.01):

Table 22: Push-pull Signal Level-High-voltage e·MMC

| Parameter           | Symbol | Min.                    | Max.                     | Unit | Conditions                           |

|---------------------|--------|-------------------------|--------------------------|------|--------------------------------------|

| Output HIGH voltage | VOH    | 0.75 * V <sub>CCQ</sub> |                          | V    | IOH = -100 μA @ V <sub>CCQ</sub> min |

| Output LOW voltage  | VOL    |                         | 0.125 * V <sub>CCQ</sub> | V    | IOL = 100 μA @ V <sub>CCQ</sub> min  |

| Input HIGH voltage  | VIH    | 0.625 * VCCQ            | V <sub>CCQ</sub> + 0.3   | V    |                                      |

| Input LOW voltage   | VIL    | VSS - 0.3               | 0.25 * V <sub>CCQ</sub>  | V    |                                      |

For 1.70V - 1.95V Vcco range (Compatible with EIA/JEDEC Standard "EIA/JESD8-7 Normal Range" as defined in the following table):

Table 23: Push-pull Signal Level-1.70 -1.95 V<sub>cco</sub> Voltage Range

| Parameter           | Symbol | Min.                      | Max.                                | Unit | Conditions |

|---------------------|--------|---------------------------|-------------------------------------|------|------------|

| Output HIGH voltage | VOH    | V <sub>CCQ</sub> - 0.45V  |                                     | V    | IOH = -2mA |

| Output LOW voltage  | VOL    |                           | 0.45V                               | V    | IOL = 2mA  |

| Input HIGH voltage  | VIH    | 0.65 * V <sub>CCQ</sub> 1 | V <sub>CCQ</sub> + 0.3              | V    |            |

| Input LOW voltage   | VIL    | V <sub>SS</sub> - 0.3     | 0.35 * V <sub>DD</sub> <sup>2</sup> | V    |            |

Note 1: 0.7 \* VDD for MMC™4.3 and older revisions.

Note 2: 0.3 \* VDD for MMC™4.3 and older revisions.

#### 8.3.3 Bus Operating Conditions for HS200 & HS400

The bus operating conditions for HS200 & HS400 devices is the same as specified in sections 10.5.1 through 10.5.2 of JESD84-B51. The only exception is that  $V_{CCQ}$ =3.3v is not supported.

#### 8.3.4 Device Output Driver Requirements for HS200 & HS400

Refer to section 10.5.4 of the JEDEC Standard JESD84-B51.

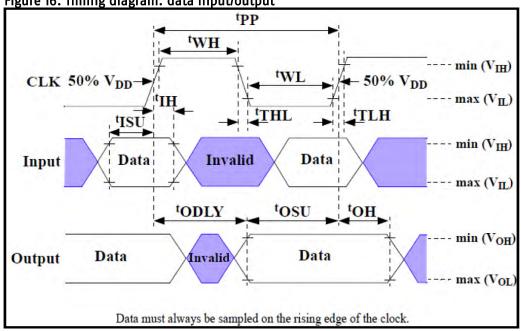

# 8.4 Bus Timing

Figure 16: Timing diagram: data input/output

#### **Device Interface Timings** 8.4.1

Table 24: High-speed Device Interface Timing

| Parameter                                            | Symbol | Min. | Max.            | Unit | Remark                           |

|------------------------------------------------------|--------|------|-----------------|------|----------------------------------|

| Clock CLK <sup>1</sup>                               |        |      |                 |      |                                  |

| Clock frequency Data Transfer Mode (PP) <sup>2</sup> | fPP    | 0    | 52 <sup>3</sup> | MHz  | CL ≤ 30 pF<br>Tolerance: +100KHz |

| Clock frequency Identification Mode (OD)             | fOD    | 0    | 400             | kHz  | Tolerance: +20KHz                |

| Clock high time                                      | tWH    | 6.5  |                 | ns   | CL ≤ 30 pF                       |

| Clock low time                                       | tWL    | 6.5  |                 | ns   | CL ≤ 30 pF                       |

| Clock rise time <sup>4</sup>                         | tTLH   |      | 3               | ns   | CL ≤ 30 pF                       |

| Clock fall time                                      | tTHL   |      | 3               | ns   | CL ≤ 30 pF                       |

| Inputs CMD, DAT (referenced to CLK)                  |        |      |                 |      |                                  |

| Input set-up time                                    | tISU   | 3    |                 | ns   | CL ≤ 30 pF                       |

| Input hold time                                      | tIH    | 3    |                 | ns   | CL ≤ 30 pF                       |

| Outputs CMD, DAT (referenced to CLK)                 |        |      |                 |      |                                  |

| Output delay time during data transfer               | tODLY  |      | 13.7            | ns   | CL ≤ 30 pF                       |

| Output hold time                                     | t0H    | 2.5  |                 | ns   | CL ≤ 30 pF                       |

| Signal rise time <sup>5</sup>                        | tRISE  |      | 3               | ns   | CL ≤ 30 pF                       |

| Signal fall time                                     | tFALL  |      | 3               | ns   | CL ≤ 30 pF                       |

-25 / 44-Confidential Rev.1.0 May 2024

Note 1: CLK timing is measured at 50% of VDD.

Note 2: e·MMC shall support the full frequency range from o-26MHz or o-52MHz

Note 3: Device can operate as high-speed Device interface timing at 26 MHz clock frequency.

Note 4: CLK rise and fall times are measured by min (VIH) and max (VIL).

Note 5: Inputs CMD DAT rise and fall times are measured by min (VIH) and max (VIL) and outputs CMD DAT rise and fall times are measured by min (VOH) and max (VOL).

Table 25: Backward-compatible Device Interface Timing

| Parameter                                            | Symbol | Min. | Max. | Unit | Remark¹    |  |  |

|------------------------------------------------------|--------|------|------|------|------------|--|--|

| Clock CLK <sup>2</sup>                               | •      |      |      |      |            |  |  |

| Clock frequency Data Transfer Mode (PP) <sup>3</sup> | fPP    | 0    | 26   | MHz  | CL ≤ 30 pF |  |  |

| Clock frequency Identification Mode (OD)             | fOD    | 0    | 400  | kHz  |            |  |  |

| Clock high time                                      | tWH    | 10   |      |      | CL ≤ 30 pF |  |  |

| Clock low time                                       | tWL    | 10   |      | ns   | CL ≤ 30 pF |  |  |

| Clock rise time <sup>4</sup>                         | tTLH   |      | 10   | ns   | CL ≤ 30 pF |  |  |

| Clock fall time                                      | tTHL   |      | 10   | ns   | CL ≤ 30 pF |  |  |

| Inputs CMD, DAT (referenced to CLK)                  |        |      |      | •    |            |  |  |

| Input set-up time                                    | tISU   | 3    |      | ns   | CL ≤ 30 pF |  |  |

| Input hold time                                      | tIH    | 3    |      | ns   | CL ≤ 30 pF |  |  |

| Outputs CMD, DAT (referenced to CLK)                 |        |      |      |      |            |  |  |

| Output set-up time <sup>5</sup>                      | tOSU   | 11.7 |      | ns   | CL ≤ 30 pF |  |  |

| Output hold time <sup>5</sup>                        | t0H    | 8.3  |      | ns   | CL ≤ 30 pF |  |  |

Note 1: The Device must always start with the backward-compatible interface timing. The timing mode can be switched to high-speed interface timing by the host sending the SWITCH command (CMD6) with the argument for high-speed interface select.

Confidential -26 / 44- Rev.1.0 May 2024

Note 2: CLK timing is measured at 50% of VDD.

Note 3: For compatibility with Devices that support the v4.2 standard or earlier, host should not use > 26 MHz before switching to high speed interface timing.

Note 4: CLK rise and fall times are measured by min (VIH) and max (VIL).

Note 5: tOSU and tOH are defined as values from clock rising edge. However, there may be Devices or devices which utilize clock falling edge to output data in backward compatibility mode. Therefore, it is recommended for hosts either to settWL value as long as possible within the range which will not go over tCK-tOH(min) in the system or to use slow clock frequency, so that host could have data set up margin for those devices. In this case, each device which utilizes clock falling edge might show the correlation either between tWL and tOSU or between tCK and tOSU for the device in its own datasheet as a note or its application notes.

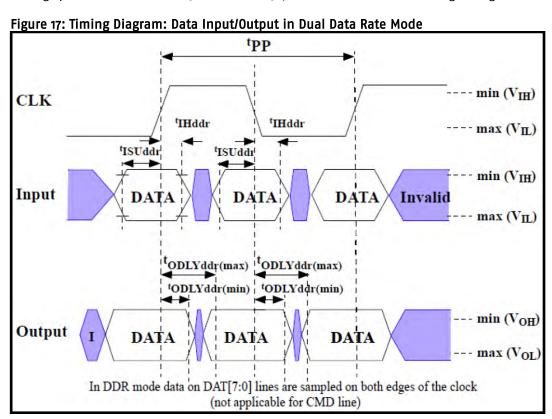

# 8.5 Bus Timing for DAT Signals During Dual Data Rate Operation

These timings apply to the DAT[7:0] signals only when the device is configured for dual data mode operation. In this dual data mode, the DAT signals operate synchronously of both the rising and the falling edges of CLK. The CMD signal still operates synchronously of the rising edge of CLK and therefore complies with the bus timing specified in section 10.5 of JESD84-B51, therefore there is no timing change for the CMD signal.

#### 8.5.1 Dual Data Rate Interface Timings

Table 26: High-speed Dual Data Rate Interface Timing

| Parameter                                   | Symbol   | Min. | Max. | Unit | Remark                       |  |  |  |

|---------------------------------------------|----------|------|------|------|------------------------------|--|--|--|

| Input CLK <sup>1</sup>                      |          |      |      |      |                              |  |  |  |

| Clock duty cycle                            |          | 45   | 55   | %    | Includes jitter, phase noise |  |  |  |

| Input DAT (referenced to CLK-DDR mode       | )        |      |      |      |                              |  |  |  |

| Input set-up time                           | tISUddr  | 2.5  |      | ns   | CL ≤ 20 pF                   |  |  |  |

| Input hold time                             | tIHddr   | 2.5  |      | ns   | CL ≤ 20 pF                   |  |  |  |

| Output DAT (referenced to CLK-DDR mod       | e)       |      |      |      |                              |  |  |  |

| Output delay time during data transfer      | tODLYddr | 1.5  | 7    | ns   | CL ≤ 20 pF                   |  |  |  |

| Signal rise time (all signals) <sup>2</sup> | tRISE    |      | 2    | ns   | CL ≤ 20 pF                   |  |  |  |

| Signal fall time (all signals)              | tFALL    |      | 2    | ns   | CL ≤ 20 pF                   |  |  |  |

Note 1: CLK timing is measured at 50% of VDD.

Note 2: Inputs CMD, DAT rise and fall times are measured by min (VIH) and max (VIL), and outputs CMD, DAT rise and fall times are measured by min (VOH) and max (VOL)

# 8.6 Bus Timing Specification in HS200 Mode

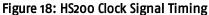

### 8.6.1 HS200 Clock Timing

Host CLK Timing in HS200 mode shall conform to the timing specified in Figure 18 and Table 27.

CLK input shall satisfy the clock timing over all possible operation and environment conditions. CLK input parameters should be measured while CMD and DAT lines are stable high or low, as close as possible to the Device.

The maximum frequency of HS200 is 200MHz. Hosts can use any frequency up to the maximum that HS200 mode allows.

Note 1:  $V_{IH}$  denote  $V_{IH}$ (min.) and  $V_{IL}$  denotes  $V_{IL}$ (max.).

Note 2:  $V_T$ =0.975V - Clock Threshold, indicates clock reference point for timing measurements.

Table 27: HS200 Clock Signal Timing

| Symbol                              | Min. | Max.                     | Unit | Remark                                                                                                                                                                                       |

|-------------------------------------|------|--------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>PERIOD</sub>                 | 5    | _                        | ns   | 200MHz (Max.), between rising edges                                                                                                                                                          |

| t <sub>TLH</sub> , t <sub>THL</sub> | -    | 0.2* t <sub>PERIOD</sub> | ns   | $t_{\text{TLH}}$ , $t_{\text{THL}}$ < 1ns (max.) at 200MHz, $C_{\text{BGA}}$ =12pF, The absolute maximum value of $t_{\text{TLH}}$ , $t_{\text{THL}}$ is 10ns regardless of clock frequency. |

| Duty Cycle                          | 30   | 70                       | %    |                                                                                                                                                                                              |

Confidential -28 / 44- Rev.1.0 May 2024

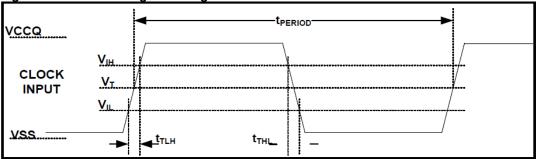

# 8.6.2 HS200 Device Input Timing

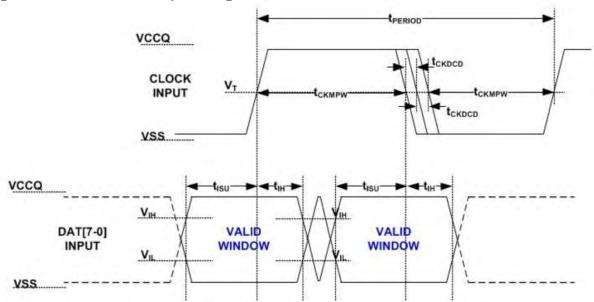

Figure 19 and Table 28 define Device input timing.

Figure 19: HS200 Device Input Timing

Note 1:  $t_{ISU}$  and  $t_{IH}$  are measured at  $V_{IL}(max.)$  and  $V_{IH}(min.)$ . Note 2:  $V_{IH}$  denote  $V_{IH}(min.)$  and  $V_{IL}$  denotes  $V_{IL}(max.)$ .

Table 28: HS200 Device Input Timing

| Symbol           | Min. | Max. | Unit | Remark                 |

|------------------|------|------|------|------------------------|

| t <sub>ISU</sub> | 1.4  | -    | ns   | $C_{BGA} \le 6pF$      |

| t <sub>IH</sub>  | 0.8  |      | ns   | C <sub>BGA</sub> ≤ 6pF |

Confidential -29 / 44- Rev.1.0 May 2024

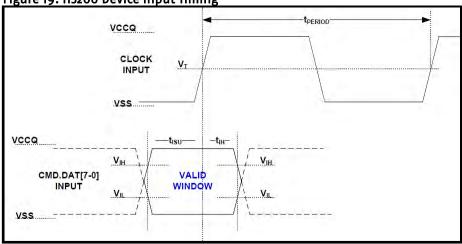

#### 8.6.3 HS200 Device Output Timing

$t_{PH}$  parameter is defined to allow device output delay to be longer than  $t_{PERIOD}$ . After initialization, the  $t_{PH}$  may have random phase relation to the clock. The Host is responsible to find the optimal sampling point for the Device outputs, while switching to the HS200 mode.

Figure 20 and Table 29 define Device output timing.

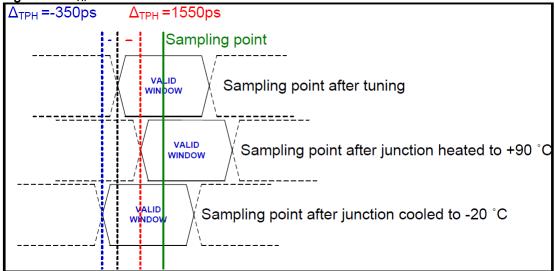

While setting the sampling point of data, a long term drift, which mainly depends on temperature drift, should be considered. The temperature drift is expressed by  $\Delta T_{PH}$ . Output valid data window ( $t_{VW}$ ) is available regardless of the drift ( $\Delta T_{PH}$ ) but position of data window varies by the drift, as described in Figure 21.

Note:  $V_{OH}$  denotes  $V_{OH}$  (min.) and  $V_{OL}$  denotes  $V_{OL}$  (max.).

Table 29: Output Timing

| Symbol          | Min.                   | Max.               | Unit | Remark                                                                                                                                                                                                                                         |

|-----------------|------------------------|--------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>PH</sub> | 0                      | 2                  | UI   | Device output momentary phase from CLK input to CMD or DAT lines output. Does not include a long term temperature drift.                                                                                                                       |

| $\DeltaT_PH$    | −350<br>(ΔT=<br>−20°C) | +1550<br>(∆T=90°C) | ps   | Delay variation due to temperature change after tuning. Total allowable shift of output valid window (Tw) from last system Tuning procedure $\Delta T_{PH}$ is 260ops for $\Delta T$ from -25°C to 85°C during operation.                      |

| T <sub>VW</sub> | 0.575                  | -                  | UI   | $t_{WW}$ =2.88ns at 200MHz Using test circuit in Figure 15 including skew among CMD and DAT lines created by the Device. Host path may add Signal Integrity induced noise, skews, etc. Expected $T_{WW}$ at Host input is larger than 0.475UI. |

Note: Unit Interval (UI) is one bit nominal time. For example, UI=5ns at 200MHz.

Figure 21:  $\Delta T_{PH}$  consideration

Implementation Guide: Host should design to avoid sampling errors that may be caused by the  $\Delta_{\text{TPH}}$  drift. It is recommended to perform tuning procedure while Device wakes up, after sleep. One simple way to overcome the  $\Delta_{\text{TPH}}$  drift is by reduction of operating frequency.

Confidential -31 / 44- Rev.1.0 May 2024

# 8.7 Bus Timing Specification in HS400 mode

## 8.7.1 HS400 Device Input Timing

The CMD input timing for HS400 mode is the same as CMD input timing for HS200 mode. Figure 22 and Table 30show Device input timing.

Figure 22: HS400 Device Data input timing

| Parameter                     | Symbol  | Min.  | Max. | Unit | Remark                                                                                             |

|-------------------------------|---------|-------|------|------|----------------------------------------------------------------------------------------------------|

| Input CLK                     |         |       |      |      |                                                                                                    |

| Cycle time data transfer mode | tPERIOD | 5     |      |      | 200MHz(Max), between rising edges with respect to VT.                                              |

| Slew rate                     | SR      | 1.125 |      | V/ns | With respect to VIH/VIL.                                                                           |

| Duty cycle<br>distortion      | tCKDCD  | 0.0   | 0.3  | ns   | Allowable deviation from an ideal 50% duty cycle. With respect to VT. Includes jitter, phase noise |

| Minimum pulse width           | tCKMPW  | 2.2   |      | ns   | With respect to VT.                                                                                |

| Input DAT (referenced to Cl   | LK)     |       |      |      |                                                                                                    |

| Input set-up time             | tISUddr | 0.4   |      | ns   | CDevice ≤ 6pF With respect to VIH/VIL.                                                             |

| Input hold time               | tlHddr  | 0.4   |      | ns   | CDevice ≤ 6pF With respect to VIH/VIL.                                                             |

| Slew rate                     | SR      | 1.125 |      | V/ns | With respect to VIH/VIL.                                                                           |

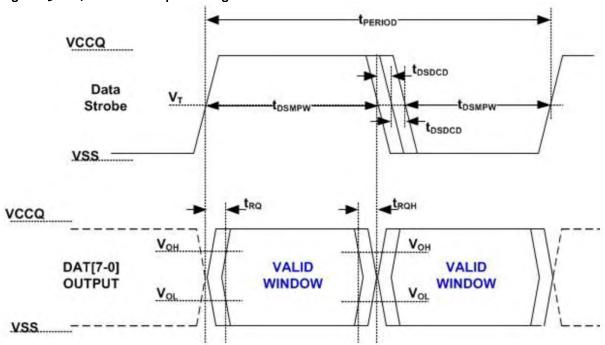

# 8.7.2 HS400 Device Output Timing

The Data Strobe is used to read data in HS400 mode. The Data Strobe is toggled only during data read or CRC status response.

Figure 23: HS400 Device output timing

Table 31 HS400 Device Output timing

| Parameter                     | Symbol       | Min.  | Max. | Unit    | Remark                                                                                                                |

|-------------------------------|--------------|-------|------|---------|-----------------------------------------------------------------------------------------------------------------------|

| Data Strobe                   |              |       |      |         |                                                                                                                       |

| Cycle time data transfer mode | tPERIOD      | 5     |      |         | 200MHz(Max), between rising edges With respect to VT                                                                  |

| Slew rate                     | SR           | 1.125 |      | V/ns    | With respect to VOH/VOL and HS400 reference load                                                                      |

| Duty cycle distortion         | tDSDCD       | 0.0   | 0.2  | ns      | Allowable deviation from the input CLK duty cycle distortion (tCKDCD) With respect to VT Includes jitter, phase noise |

| Minimum pulse width           | tDSMPW       | 2.0   |      | ns      | With respect to VT                                                                                                    |

| Read pre-amble                | tRPRE        | 0.4   | -    | tPERIOD | Max value is specified by manufacturer.<br>Value up to infinite is valid                                              |

| Read post-amble               | tRPST        | 0.4   | -    | tPERIOD | Max value is specified by manufacturer.<br>Value up to infinite is valid                                              |

| Output DAT (referenced to     | Data Strobe) |       |      |         |                                                                                                                       |

| Output skew                   | tRQ          |       | 0.4  | ns      | With respect to VOH/VOL and HS400 reference load                                                                      |

| Output hold skew              | tRQH         |       | 0.4  | ns      | With respect to VOH/VOL and HS400 reference load.                                                                     |

| Slew rate                     | SR           | 1.125 |      | V/ns    | With respect to VOH/VOL and HS400 reference load                                                                      |

Confidential -33 / 44- Rev.1.0 May 2024

Table 32: HS400 Capacitance and Resistors

| Parameter                               | Symbol  | Min. | Туре | Max. | Unit | Remark |

|-----------------------------------------|---------|------|------|------|------|--------|

| Pull-up resistance for CMD              | RCMD    | 4.7  |      | 100  | k0hm |        |

| Pull-up resistance for DATo-7           | RDAT    | 10   |      | 100  | k0hm |        |

| Pull-down resistance for Data<br>Strobe | RDS     | 10   |      | 100  | k0hm |        |

| Internal pull up resistance DAT1-DAT7   | Rint    | 10   |      | 150  | k0hm |        |

| Single Device capacitance               | CDevice |      |      | 6    | pF   |        |

# 9. e·MMC Registers

Within the Device interface six registers are defined: OCR, CID, CSD, EXT\_CSD, RCA and DSR. These can be accessed only by corresponding commands (see Section 6.10 of JESD84-B51).

Table 33: e·MMC Registers

| Name    | Width<br>(Bytes) | Description                                                                                                                       | Implementation            |

|---------|------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| CID     | 16               | Device Identification number, an individual number for identification.                                                            | Mandatory                 |

| RCA     | 2                | Relative Device Address is the Device system address, dynamically assigned by the host during initialization.                     | Mandatory                 |

| DSR     | 2                | Driver Stage Register, to configure the Device's output drivers.                                                                  | Optional, not implemented |

| CSD     | 16               | Device Specific Data, information about the Device operation conditions.                                                          | Mandatory                 |

| OCR     | 4                | Operation Conditions Register. Used by a special broadcast command to identify the voltage type of the Device.                    | Mandatory                 |

| EXT_CSD | 512              | Extended Device Specific Data. Contains information about the Device capabilities and selected modes. Introduced in standard v4.0 | Mandatory                 |

The host may reset the device by:

- Switching the power supply off and back on. The device shall have its own power-on detection circuitry which puts the device into a defined state after the power-on Device.

- A reset signa

- By sending a special command

# 9.1 OCR Register

The 32-bit operation conditions register (OCR) stores the VDD voltage profile of the Device and the access mode indication. In addition, this register includes a status information bit. This status bit is set if the Device power up procedure has been finished. The OCR register shall be implemented by all Devices.

Table 34: OCR register

| <u> </u> | Table 5 II out register                     |                                     |  |  |  |  |

|----------|---------------------------------------------|-------------------------------------|--|--|--|--|

| OCR bit  | V <sub>CCQ</sub> voltage window             | typ. value                          |  |  |  |  |

| [6:0]    | Reserved                                    | 000 0000b                           |  |  |  |  |

| [7]      | 1.70 - 1.95V                                | 1b                                  |  |  |  |  |

| [14:8]   | 2.0 - 2.6V                                  | 000 0000b                           |  |  |  |  |

| [23:15]  | 2.7 - 3.6V                                  | 1 1111 1111b                        |  |  |  |  |

| [28:24]  | Reserved                                    | o oooob                             |  |  |  |  |

| [30:29]  | Access Mode                                 | 10b (sector mode, for devices >2GB) |  |  |  |  |

| [31]     | Card power up status bit (o=busy; 1=ready)¹ |                                     |  |  |  |  |

Note 1: This bit is set to LOW if the Device has not finished the power up routine.

Confidential -34 / 44- Rev.1.0 May 2024

### 9.1.1 Memory Addressing

Previous implementations of the e·MMC specification (versions up to v4.1) implemented byte addressing using a 32 bit field. This addressing mechanism permitted for e·MMC densities up to and including 2 GB.

To support larger densities the addressing mechanism was update to support sector addresses (512 B sectors). The sector addresses shall be used for all devices with capacity larger than 2 GB.

To determine the addressing mode use the host should read bit [30:29] in the OCR register.

# 9.2 CID Register

The Card Identification (CID) register is 128 bits wide. It contains the Device identification information used during the Device identification phase (e·MMC protocol). For details, refer to section 7.2 of the JEDEC Standard JESD84-B51.

Table 35: CID register

| Register Name | Bit Width | Description               | typ. Value  |

|---------------|-----------|---------------------------|-------------|

| MID           | 8         | Manufacture ID            | 0x52        |

| _             | 6         | Reserved                  | 000000      |

| СВХ           | 2         | Device/BGA                | 01          |

| OID           | 8         | OEM/Application ID        | 0x52        |

| PNM           | 48        | Product Name 5GB          | "AS005G"    |

|               | , ,       | Product Name 10GB         | "AS010G"    |

| PRV           | 8         | Product Revision          | 0x11        |

| PSN           | 32        | Product Serial Number     | xxxxxxx     |

| MDT           | 8         | Manufacture Date          | XX          |

| CRC           | 7         | Check sum of CID contents | CRC7 chksum |

| -             | 1         | Not used; always=1        | 1           |

## 9.3 CSD Register

The Device-Specific Data (CSD) register provides information on how to access the Device contents. The CSD defines the data format, error correction type, maximum data access time, data transfer speed, whether the DSR register can be used etc. For details, refer to section 7.3 of the JEDEC Standard JESD84-B51.

Table 36: CSD register

| Register Name      | Bits    | Bit Width | Description                                     | typ. Value |

|--------------------|---------|-----------|-------------------------------------------------|------------|

| CSD_STRUCTURE      | 127:126 | 2         | CSD structure                                   | 0x3        |

| SPEC_VERS          | 125:122 | 4         | System Specification version                    | 0x4        |

| -                  | 121:120 | 2         | Reserved                                        | -          |

| TAAC               | 119:112 | 8         | Data read access-time 1                         | 0X27       |

| NSAC               | 111:104 | 8         | Data read access-time 2 in CLK cycle (NSAC*100) | OX01       |

| TRAN_SPEED         | 103:96  | 8         | Max. bus clock frequency                        | 0X32       |

| ССС                | 95:84   | 12        | Device command classes                          | oxoF5      |

| READ_BL_LEN        | 83:80   | 4         | Max. read data block length                     | 0X9        |

| READ_BL_PARTIAL    | 79      | 1         | Partial blocks for read allowed                 | 0x0        |

| WRITE_BLK_MISALIGN | 78      | 1         | Write block misalignment                        | 0x0        |

| READ_BLK_MISALIGN  | 77      | 1         | Read block misalignment                         | 0X0        |

| DSR_IMP            | 76      | 1         | DSR implemented                                 | 0X0        |

| -                  | 75:74   | 2         | Reserved                                        | -          |