10/01/2024 rev: 1.0

#### Table of Contents

- 1. Introduction

- 2. Form Factor

- Pin Definition

Block Diagram

Power Design Constraint

- 6. PCIe Key Features 7. Thermal

- 8. Use Cases

- 9. Ordering Information 10. Revision History

- 11. Legal Disclaimer

## 1. Introduction

This datasheet details the design and configuration of MemryX's M.2 AI Acceleration Module (hereafter referred to as M.2 Module). The M.2 Module enables high performance, yet power-efficient AI inference for edge devices and edge servers. The M.2 Module is an ideal companion module for offloading the processing of deep neural network (DNN) computer vision (CV) models from the Host CPU. Its unique dataflow architecture excels in performing real-time, low latency neural network inference while saving system power.

The M.2 Module is based on MemryX's MX3 AI Accelerator IC. The M.2 Module's industry compliant PCIe Gen 3 connectivity supports high throughput for streaming input data and inference results to the Host processor. Its industry compliant M.2 2280 compact form-factor simplifies installation into a wide selection of Host platforms.

#### Features

- Four (4) MemryX MX-3TM "digital at-memory compute" AI ASICs

Dataflow architecture optimized for high throughput, low latency applications

- Advanced power management

- Up to 20 TFLOPs dependent on available power

Up to 80 million weight (4-bit) parameters

Model parameters and matrix operators stored on-chip

- · 2/4-lane PCIe Gen3 for up to 4GT/s bandwidth

- · Multi-stream and multi-model support

- Floating-point activations for high accuracy

Support for hundreds of AI models with no re-tuning required

- PyTorch, TensorFlow, Keras and ONNX model support

- OS Support for Windows 10/11 64-bit, Ubuntu 18.04 and later 64-bit

### Specifications

| SYSTEM                         |                              |  |

|--------------------------------|------------------------------|--|

| AI Processor                   | MemryX MX3 (x4)              |  |

| Host Processor Support         | ARM, x86, RISC-V             |  |

| ELECTRICAL                     |                              |  |

| Input Voltage                  | 3.3V +/- 5%                  |  |

| Interface                      | PCIe Gen 3, 2 x 2-lanes      |  |

| MECHANICAL                     |                              |  |

| Form Factor                    | NGFF M.2-2280-D5-M, Socket 3 |  |

| Dimensions                     | 3.15" x 0.87" (22 x 80 mm)   |  |

| ENVIRONMENTAL                  |                              |  |

| Operating Temperature 0°-70° C |                              |  |

| COMPLIANCE                     |                              |  |

| Certification                  | CE / FCC Class A, RoHS       |  |

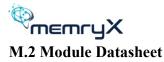

# 2. Form Factor

The M.2 Module is designed to be compliant with M.2-2280-D5-M form factor defined in the spec. Refer to below table for the nomenclature and actual board picture/size.

## 3. Pin Definition

This pinout table and I/O direction is defined in the perspective of module, not baseboard perspective. Pin definition is compatible to PCI-SIG M.2 specification for M-key applications.

| 74 | 3.3V                     | GND        | 75 |

|----|--------------------------|------------|----|

|    |                          | GND        | 73 |

| 72 | 3.3V                     | GND        | 71 |

| 70 | 3.3V                     | N/C        | 69 |

| 68 | N/C                      | N/C        | 67 |

|    | Module Key<br>Module Key | Module Key |    |

|    | Module Key               | Module Key |    |

|    |                          | Module Key |    |

|    | Module Key               | Module Key |    |

| 58 | N/C                      | GND        | 57 |

| 56 | N/C                      | REFCLKp    | 55 |

| 54 | PEWAKE# (I/O)(0/3.3V)    | REFCLKn    | 53 |

| 52 | CLKREQ# (I/O)(0/3.3V)    | GND        | 51 |

| 50 | PERST# (I)(0/3.3V)       | PERp0      | 49 |

| 48 | N/C                      |            | 43 |

| 46 | N/C                      | PERnO      |    |

| 44 | N/C                      | GND        | 45 |

| 42 | N/C                      | PETp0      | 43 |

| 40 | N/C                      | PETn0      | 41 |

| 38 | N/C                      | GND        | 39 |

| 36 | N/C                      | PERp1      | 37 |

|    |                          | PERn1      | 35 |

| 34 | N/C                      | GND        | 33 |

| 32 | N/C                      |            |    |

| 30 | N/C  | PETp1 | 31 |

|----|------|-------|----|

|    |      | PETn1 | 29 |

| 28 | N/C  | GND   | 27 |

| 26 | N/C  | PERp2 | 25 |

| 24 | N/C  | PERn2 | 23 |

| 22 | N/C  | GND   | 21 |

| 20 | N/C  | PETp2 | 19 |

| 18 | 3.3V | PETn2 | 17 |

| 16 | 3.3V |       | 17 |

| 14 | 3.3V | GND   | _  |

| 12 | 3.3V | PERp3 | 13 |

| 10 | N/C  | PERn3 | 11 |

| 8  | N/C  | GND   | 9  |

| 6  | N/C  | PETp3 | 7  |

| 4  | 3.3V | PETn3 | 5  |

| 2  | 3.3V | GND   | 3  |

| 2  | 3.37 | GND   | 1  |

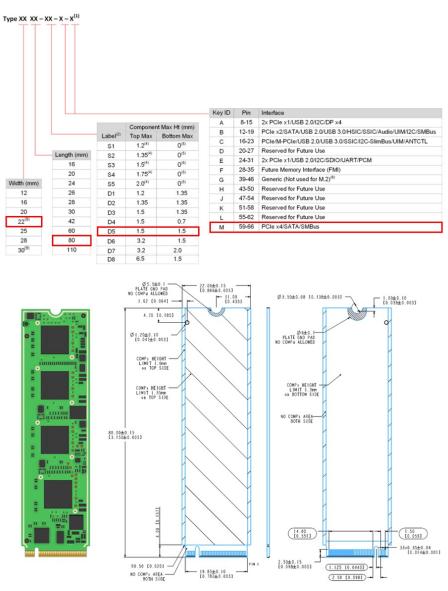

## 4. Block Diagram

Below is the block diagram of the M.2 Module.

## 5. Power Design Constraint

The M.2 Specification restricts current draw to 500mA/pin. With nine power pins, that is a limit of 4500mA, or 14.85W power dissappation. The M.2 module uses current sensing to insure the power does not exceed the limit. Some older motherboards do not provide power to all nine pins, so they cannot support the full power. If there is an issue ennumerating or running inference, try a newer motherboard.

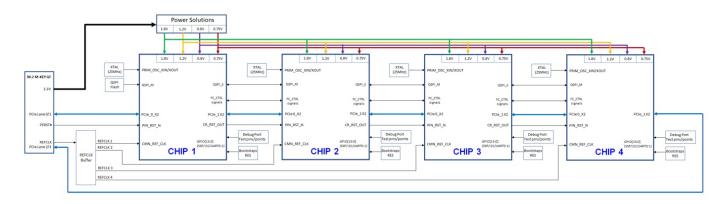

## 6. PCIe Key Features

In normal operation, Chip 1 receives input (video or image stream for CV applications) data from the external Host processor via a PCIe connection. The Host processor expects an inference result in return. If Chip 1 is able to run all the layers of AI model on its own, it will process the data and return a result to the Host using the same bidirectional PCIe link. If the model uses 2 or 3 chips, the data is sent from Chip 1 to Chip 2 and, if required, to Chip 3. The inference result is sent back to the Host via the same PCIe path but in the reverse direction. If the model uses all 4 chips, instead of sending the result in the reverse direction through Chips 1-3, the result can be sent directly from Chip 4's output PCIe port to the M.2 connector to the Host.

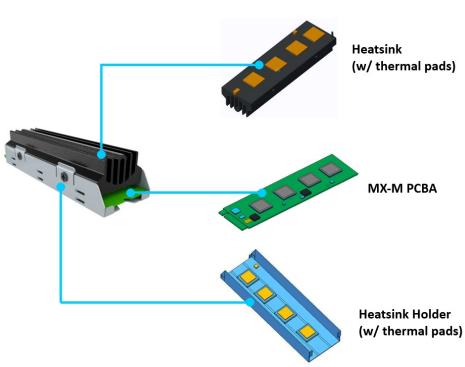

# 7. Thermal

This section shows the thermal solution using on the M.2 Module for heat dissipation. Here are four simulated cases based on different conditions to showcase the capability of M.2 Module and thermal solution.

| Cases                     | 1      | 2      | 3         | 4         |

|---------------------------|--------|--------|-----------|-----------|

| Condition                 | Worst  | Normal | Low Power | Low Power |

| System TDP                | 14.85W | 11.55W | 7.115W    | 4.876W    |

| Ambient Temp              | 70C    | 70C    | 40C       | 25C       |

| Heatsink                  | Yes    | Yes    | Yes       | No        |

| Airflow Requirement (Min) | 1 CFM  | 0.8CFM | 0 CFM     | 0 CFM     |

## 8. Use Cases

This section demonstrates several use cases of M.2 Module.

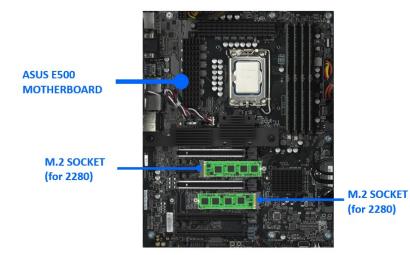

#### 8.1 M.2 socket on Mother board

Many motherboards have two or more M.2 slots. One is typically used to boot from SSD, and the other could be used for the M.2 accelerator. If there is only one slot and its occupied by an SSD M.2 module, it might be possible to configure the motherboard to boot from a SATA SSD instead, freeing up the M.2 slot for the accelerator. If not, see section 8.2 for another solution.

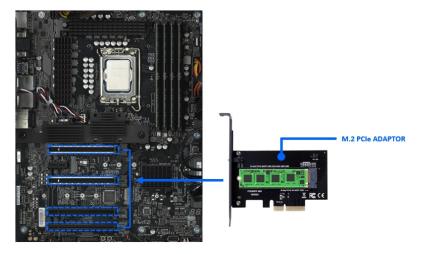

#### 8.2 PCIe-M.2 adaptor on Mother board standard PCIe slot

If there is no M.2 slot on the motherboard, a PCIe adapter board can be used to mount the M.2 module.

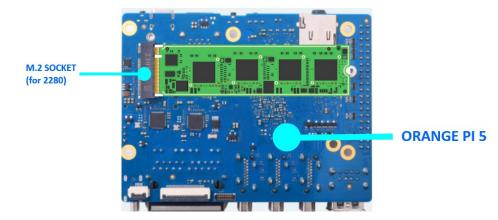

#### 8.3 M.2 socket on embedded systems

Orange Pi 5 is a small embedded system with one M-key M.2 socket, which is a good development platform.

### 9. Ordering Information

| PART NUMBER    | DESCRIPTION                                         |

|----------------|-----------------------------------------------------|

| MX3-2280-M-4-C | 4-chip M.2 module, 22x80 mm, M-Key, Commercial Temp |

### **10. Revision History**

| Date       | Version | Revision                        |

|------------|---------|---------------------------------|

| 2023.11.06 | 0.1     | Initial release.                |

| 2023.12.15 | 0.2     | Updated                         |

| 2024.07.23 | 0.3     | Internal Release for Review     |

| 2024.07.24 | 0.31    | Release for Public Distribution |

| 2024.10.03 | 1.0     | Production Release              |

# 11. Disclaimer and Proprietary Information Notice

### 11.1 Copyright

© 2024 MemryX All rights reserved. No part of this document may be reproduced or transmitted in any form without the express, written permission of MemryX. Nothing contained in this document should be construed as granting any license or right to use proprietary information without the written permission of MemryX. This version of the document supersedes all previous versions.

#### **11.2 General Notice**

To the fullest extent permitted by law, MemryX provides this document "as is" and disclaims all warranties, either express or implied, statutory, or otherwise, including but not limited to the warranties of merchantability, non-infringement of third-party rights, and fitness for particular purposes. This document may inadvertently contain technical inaccuracies or other errors. MemryX assumes no liability for any such errors and for damages, whether direct, indirect, incidental, consequential, or otherwise, that may result from such errors, including but not limited to loss of data or profits. The content in this document is subject to change without notification to users.